新聞動態

news and trends

新聞動態

news and trends2023-04-26 來源:Carbontech

由于SiC MOSFET具有取代現有的硅超級結(SJ)晶體管和集成柵雙極晶體管(IGBT)技術的潛力,因此受到了特別的關注。2010年以來,碳化硅功率MOSFET市場顯著擴大,現在每年超過2億美元。尤其是隨著SiC在汽車、光伏、鐵路等多個市場取代硅技術,許多新的參與者已經進入市場,有望實現兩位數的復合年增長率。

通常,SiC 功率MOSFET的工作電壓為1200或1700 V,旨在取代IGBT技術。但SiC MOSFET 有它的一些問題,其中大部分與柵氧化層直接相關。另外,寬禁帶器件的一個問題是,在反向偏置過程中,在柵極氧化物處有更高的電場。為了利用碳化硅的高擊穿能力,緩解柵極氧化物處的電場是必要的。為了改善這一問題,在源極溝槽的底部采用具有p型區域的雙溝槽結構,它比柵極溝槽的底部更深。單溝槽和雙溝槽的仿真結果中,雙溝槽結構的溝槽底部電場濃度更低,這種結構防止了對柵極溝槽處的氧化層破壞。通過引入溝槽結構,可以有效地降低了電場,從而提高了器件性能。

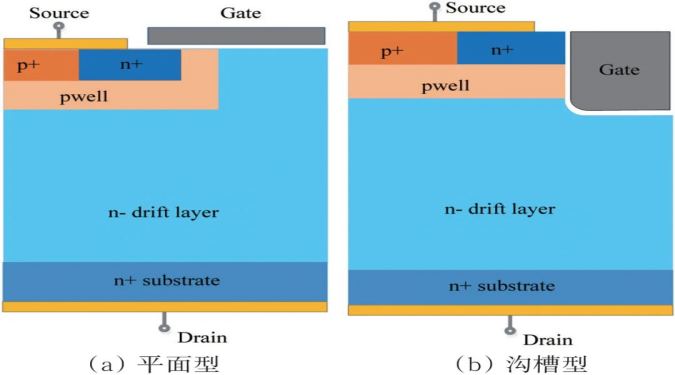

SiC功率MOSFET通常采用平面結構或者溝槽結構,在650~3300 V電壓范圍內已形成成熟的產品技術。目前SiC MOSFET的發展趨勢有四個方向:更小的元胞尺寸,更低的比導通阻,更低的開關損耗,更好的柵氧保護,提高器件的性能和可靠性。

平面型 OR 溝槽型?

SiC MOSFET自2010年Cree和ROHM推出1G以來,平面柵結構一直被使用,但平面柵結構限制了元胞間距的減小速率,預計在更高代次的產品中溝槽柵結構將取代平面柵結構。功率晶體管由很多個元胞組成,這些元胞以間距大小Cell Pitch為特征。技術擴展旨在減少晶體管元胞間距。

RONxA表示芯片每平方毫米的導通電阻,通常用mΩ x mm2單位表示。對于垂直晶體管,RONxA取決于晶體管布局、垂直結構和雜質摻雜分布設計。RONxA越小,芯片尺寸越小,同時降低了成本/價格、晶體管電容、動態損耗和開關延遲時間。

與高級邏輯CMOS一樣,功率晶體管技術的發展是由降低成本和提高性能的需求推動的。這些目標是通過開發新的晶體管結構和縮小尺寸來實現的,對于恒定的Ron值,芯片面積每三年比上一代減小0.7倍。自2016年以來,領先制造商已推出商用溝槽柵SiC MOSFET,更小的元胞尺寸給這些器件的可靠性和魯棒性帶來了新的挑戰。

典型的SiC MOSFET結構

SiC MOSFET平面結構:特點是工藝簡單,單元的一致性較好,雪崩能量比較高。但是,這種結構的中間,N區夾在兩個P區域之間,當電流被限制在靠近P體區域的狹窄的N區中流過時,將產生JFET效應,從而增加通態電阻;同時,這種結構的寄生電容也較大。

SiC MOSFET溝槽結構:是將柵極埋入基體中形成垂直溝道,盡管其工藝復雜,單元一致性比平面結構差。但是,溝槽結構可以增加單元密度,沒有JFET效應,寄生電容更小,開關速度快,開關損耗非常低;而且,通過選取合適溝道晶面以及優化設計的結構,可以實現最佳的溝道遷移率,明顯降低導通電阻,因此,新一代SiC MOSFET主要研究和采用這種結構。

目前,SiC MOSFET溝道遷移率低的問題仍然比較突出,對于中低壓器件(650~1700 V)溝道電阻占總導通電阻的比例較高。

相對而言,平面柵SiC MOSFET工藝復雜度沒那么高,而且開發歷史比較長,國內外相關產品較早實現量產,并且在特拉斯、比亞迪等眾多車企帶動下,平面柵SiC MOSFET功率模塊自2018年就進入了主驅逆變器。

溝槽柵SiC MOSFET的發展則較為緩慢,主要受限于工藝水平和柵氧可靠性等問題,比如柵極溝槽底部電場集中,通常會引發長期可靠性問題。盡管如此,國內外依舊有眾多的企業和機構在研發溝槽柵 SiC MOSFET,因為這種結構理論上,可以最大限度地發揮SiC材料的特性,尤其是可以進一步降低器件成本和導通電阻。目前碳化硅器件的價格仍然是硅器件的4倍左右,因此僅在一些對體積和效率要求比較高的場景,SiC MOSFET的滲透率會快一些,所以亟需降低成本以加速打入更多應用場景。

目前,市場上這兩種結構應用比較典型的是羅姆和英飛凌科采用溝槽結構SiC MOSFET,溝槽型沒有結型場效應晶體管(JFET)區,具有更高的溝道密度,同時溝道所在SiC晶面具有較高的溝道遷移率,因此能夠實現更低的比導通電阻。而Cree和意法半導體兩家公司采用平面結構SiC MOSFET,通過優化器件的結構設計,實現了性能和可靠性俱佳的產品技術,得到了廣泛的應用。接下來,我們來具體看下巨頭們的技術路線選擇。

巨頭們的選擇

英飛凌:半包溝槽結構

英飛凌的半包溝槽結構是業界不多的幾個能夠量產上車的碳化硅溝槽結構設計。例如,英飛凌CoolSiC? MOSFET采用了不對稱的溝槽結構,該結構中MOS溝道選擇了最有利的方向。

今年,英飛凌對外宣布目前已有的碳化硅訂單使得2022財年來自碳化硅產品的收入超過去年近一倍,沖擊3億歐元。預測到2025年前后碳化硅功率器件產品線可以為公司帶來10億美元左右的營收。

目前已經開始英飛凌貢獻碳化硅產品營收的客戶包括現代集團,其Ioniq 5電動緊湊型休旅車采用緯湃科技Vitesco提供的800V逆變器,內部使用的碳化硅模塊即來自英飛凌。與此同時,英飛凌還是小鵬汽車的碳化硅模塊的主要提供商,用于旗艦SUV車型G9中,預計今年第3季度起正式交付。

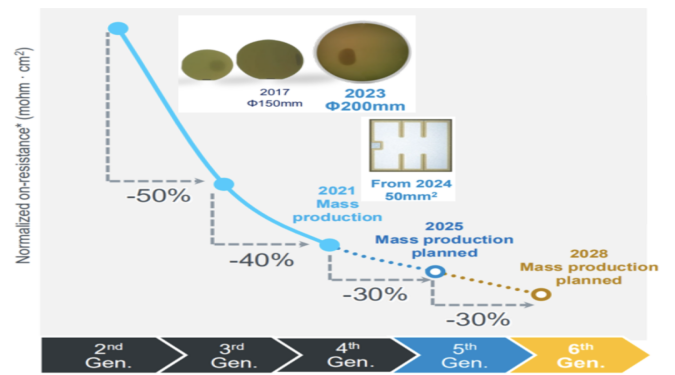

羅姆:第四代雙溝槽將成為主力

據公開消息,羅姆目前已經規劃在2021年至2025年的5年間,投入1200億至1700億日元(10億-13億美元)的資金,將碳化硅產能擴充至少6倍。

在碳化硅器件技術方面羅姆也處于領先地位。2010 年公司就開始量產首款碳化硅MOSFET,與之后推出的第2代產品都采用平面柵極設計。2015年羅姆又領先競爭對手,率先量產雙溝槽結構的第3代產品。目前,ROHM公司開發出了雙溝槽MOSFET結構,該結構同時具有源極溝槽和柵極溝槽。

FUJI公司:P阱覆蓋溝槽底部溝槽底部的柵極氧化物的結構

采用了一種用P阱覆蓋溝槽底部溝槽底部的柵極氧化物的結構,同時減小了cell pitch并優化了MOS溝道長度及JFET區域。該結構使得溝槽底部P阱底角部分的電場達到最大值,從而使得柵極氧化物中的電場得到松弛。為了同時建立高閾值電壓和低導通電阻,設計減少了cell pitch并優化了MOS溝道長度,隨著cell間距的收縮,在導通狀態下電阻比例降低。為了同時建立低導通電阻和高擊穿電壓,將JFET區域優化在溝槽底部P阱和源極接觸點下方之間的區域。通過對這種結構的優化,使得導通電阻降低了3%的同時提高2%的擊穿電壓。

Mitsubishi公司:溝槽型SiC-MOSFET,采用了獨特電場限制結構

在垂直溝槽方向注入鋁元素,使溝槽底部形成電場限制層,再通過其新技術斜向注入鋁,形成連接電場場限制層和源極的側接地,并斜向注入氮元素,再局部形成更容易導電的高濃度摻雜層。電場限制層將施加在柵極絕緣膜上的電場降低到傳統平面結構水平,保證耐壓的同時,提高器件的可靠性。連接電場限制層和源極的側接地,實現了高速開關動作,減少開關損耗。與平面結構相比,溝槽型器件Cell pitch更小,所以功率器件能排列更多的元胞。元胞高密度排列使得流動的電流變多,但各柵極的之間的間隔太小就會導致路徑變窄,電流流動困難。將氮元素斜向注入,在局部形成更容易導電的高濃度摻雜層,使電流路徑上的電流變得容易傳輸,從而降低電流通路的電阻。與沒用高濃度層相比,電阻率降低了約25%。

HestiaPower公司:提出了一種結勢壘肖特基二極管集成碳化硅MOSFET

將DMOS和結勢壘肖特基二極管(JBS)合并到單片SiC器件中,分別在n+/p+區形成歐姆接觸,在漂移層形成肖特基接觸,在MOSFET的有源區形成嵌入JBS。

JMOS器件比傳統SiC DMOS具有更低的反向導通壓降,VSD改善了47%。在動態性能方面也具有優越性,反向恢復電荷(Qrr)降低54%,最大反向恢復電流(IRMax)降低40%。當SiC MOSFET中的寄生體二極管開啟時,集成JBS還可以防止由于注入的少數載流子的復合而導致的位錯缺陷轉變為層錯而導致的潛在失效。且無需任何附加工藝和面積損失,是一種成本效益高的方法。

意法半導體:深挖平面潛力,布局溝槽

根據意法半導體在近期財報中透露的最新數據,截止2022財年第1季度,公司碳化硅產品已經在75個客戶的98個項目中送樣測試,其中工業應用和電動汽車應用各占一半。

意法在碳化硅研發上繼續投入相當資源。在生產技術上,意法于2021年年中宣布其挪威分部STMicroelectronics Silicon Carbide A.B. 開始進行8寸碳化硅材料的實驗室制造,預計相應技術將在2025年前后成熟,并應用到規劃中的新加坡8寸碳化硅生產線中。

在芯片設計上意法繼續深挖平面設計碳化硅MOSFET的技術潛力,推出了第4代平面柵碳化硅,并在今年第二季度量產。而之前規劃的溝槽柵設計產品則順延成為意法的第5代碳化硅MOSFET,目前應該在工程樣品測試階段,量產時間待定。相比上一代產品,第4代平面柵碳化硅的性能有所進步,包括導通電阻減少15%,工作頻率增加一倍至1MHz。

Wolfspeed:平面柵SiC MOSFET的技術優勢遠未耗盡

6月27日,德國媒體Elektroniknet發布了一篇采訪Wolfspeed聯合創始人John Palmour博士的文章。報道稱,John Palmour從一開始就致力于碳化硅二極管和MOSFET的開發,作為Wolfspeed的CTO,他認為平面柵SiC MOSFET的技術優勢遠未耗盡。

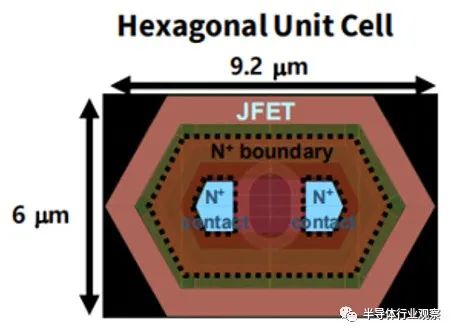

Wolfspeed累積的Design-in金額在87億美元這個驚人的水平,其中包括大眾集團“未來汽車供應路線(FAST)”計劃和通用汽車奧騰能平臺項目。另外,市場也傳言戴姆勒集團和奧迪的下一代E-tron車型也選擇了Wolfspeed的產品。Wolfspeed的碳化硅MOSFET采用平面設計,目前處于第3代(Gen 3),涵蓋650V到1200V之間的多個電壓規格。與之前兩代產品相比,Gen 3 平面MOSFET采用六邊形晶胞微觀設計,650V Gen 3和1200V Gen 3+的單位面積導通電阻分別為2.3 m?·cm2和2.7 m?·cm2,較上一代Strip Cell減少了16%。目前Wolfspeed的Gen 4 溝槽柵仍在開發中,具體量產時間還沒有透露。

2022年溝槽柵SiC MOSFET快速上車,布局行業市場

除了羅姆外、英飛凌、博世、電裝等眾多國內外企業都在開發溝槽柵產品,且多家企業的產品已經成功量產,意法半導體、安森美等企業也在布局開發自己的溝槽柵SiC MOSFET。

2022年,SiC MOSFET繼續上車。據公開報道不完全統計,今年1-7月,全球新增了多款SiC車型,包括:豐田旗下的雷克薩斯RZ、現代旗下IONIQ6、吉利旗下的Smart精靈#1以及蔚來旗下的ES7等。除了蔚來外,上述車型都采用了溝槽柵SiC MOSFET供應商,包括電裝、博世、英飛凌、羅姆。

截至目前,豐田、現代和吉利等多家車企的主驅都已采用溝槽柵SiC MOSFET,其供應商包括電裝、英飛凌、博世和羅姆等。中國方面,多家公司也將溝槽SiC MOSFET作為技術開發重點,甚至已有一家國內企業已經量產了溝槽SiC MOSFET,其成本相比平面SiC MOSFET可降低40%。目前該產品正在進行上車驗證,預計明年即將在國內的自有晶圓廠完成流片。

另外,從今年上車的情況來看,博世、英飛凌和羅姆等企業似乎已經針對溝槽柵SiC MOSFET的可靠性課題,找到了緩和柵極溝槽底部的電場集中問題的技術和工藝,來確保產品長期可靠性。目前,我國的安海半導體在2022年初成功研發出第一代溝槽柵SiC MOS,單芯片內阻達到新能源主驅應用級別:1200V 15mΩ的SiC MOSFET,芯片面積相較目前國外知名品牌同規格的SiC MOS都要小(單芯片面積小于20mm2),目前已實現量產,正在上車驗證中。另外,安海第二代溝槽柵SiC MOS也正在研發中,有望于2023年初在國內自有晶圓廠完成流片。

當然,設計、制造高性能的溝槽柵SiC MOSFET也是我國SiC功率器件發展的當務之急,部分企業、事業單位已經將研究的重心轉移至溝槽柵SiC MOSFET,比如杭州電子科技大學、香港科技大學等。

溝槽是潮流,一定要做溝槽?

對于是否一定要做溝槽問題,我們需要考慮理論可行性和實際市場需求問題。

不管Si IGBT還是Si MOSFET,溝槽柵結構的設計相比于平面柵結構具有明顯的性能優勢,但是對于SiC MOSFET來說,目前這種優勢不再顯著。

從理論上來看,平面柵 SiC MOSFET的溝道遷移率低,相較之下,溝槽柵SiC MOSFET則呈現出更佳的電學特性,其優勢包括:元胞密度高、導通損耗低、開關性能強等。

根據高斯定理,SiC MOSFET中柵極SiO2表面承受的電場強度約是其對應的SiC表面電場強度的2.5倍,由于碳化硅材料以高臨界擊穿電場強度著稱(約為硅材料的10倍),所以SiC MOSFET中柵極SiO2承受的電場強度極高,比Si MOSFET/IGBT中柵極SiO2承受的電場強度高一個數量級。因此,SiC MOSFET的大部分問題都與柵氧化層直接相關。

例如,SiC MOSFET 柵極氧化層的可靠性問題。溝槽柵SiC MOSFET更加嚴重,因為接近90°的溝槽柵拐角進一步加劇了電力線的集中,此處的柵氧層極易被擊穿。

解決柵極氧化層可靠性問題是目前所有的溝槽柵SiC MOSFET結構設計必須首先解決的問題,已有技術路線是設計額外的JFET區,通過其耗盡區的“夾斷”來屏蔽保護中間的柵極氧化層,減少溝槽柵拐角位置氧化層承受的電應力,但這同時也引入了很大的JFET電阻,導通電阻因此顯著增加。

總的來說,平面型SiC MOSFET由于具備天然的可靠性優勢,更容易被市場認可。當然,如果未來柵極介質層的可靠性問題得到徹底解決,更緊湊的溝槽型SiC MOSFET仍然具有巨大的發展潛力。

但是,客戶關心的并不是它究竟是平面MOSFET還是溝槽MOSFET,更重要的是特定導通電阻。事實上,我們也不在乎哪種技術路線,我們只關注哪種設計能給客戶帶來最大的利益。“簡而言之,平面結構還有深挖的空間,國內企業深耕平面型,做好可靠性,也一樣有市場!